PCIe 7.0のver0.9が定められたことで、ほとんどの仕様が確定しました。実際に一般ユーザーに普及するまではまだまだ時間がかかりますが、その性能には要注目です。

Contents

PCIe 7.0とは?新世代高速インターフェースの詳細技術とPCIe 5.0との違い

PCI Express(PCIe)はパソコン内部でデータをやり取りするための重要なインターフェース規格であり、次々と進化しています。この記事では、最新のPCIe 7.0規格について解説します。そのうえで、現行のPCIe 5.0との違いについても述べていきます。

PCIe規格はどのように策定される?

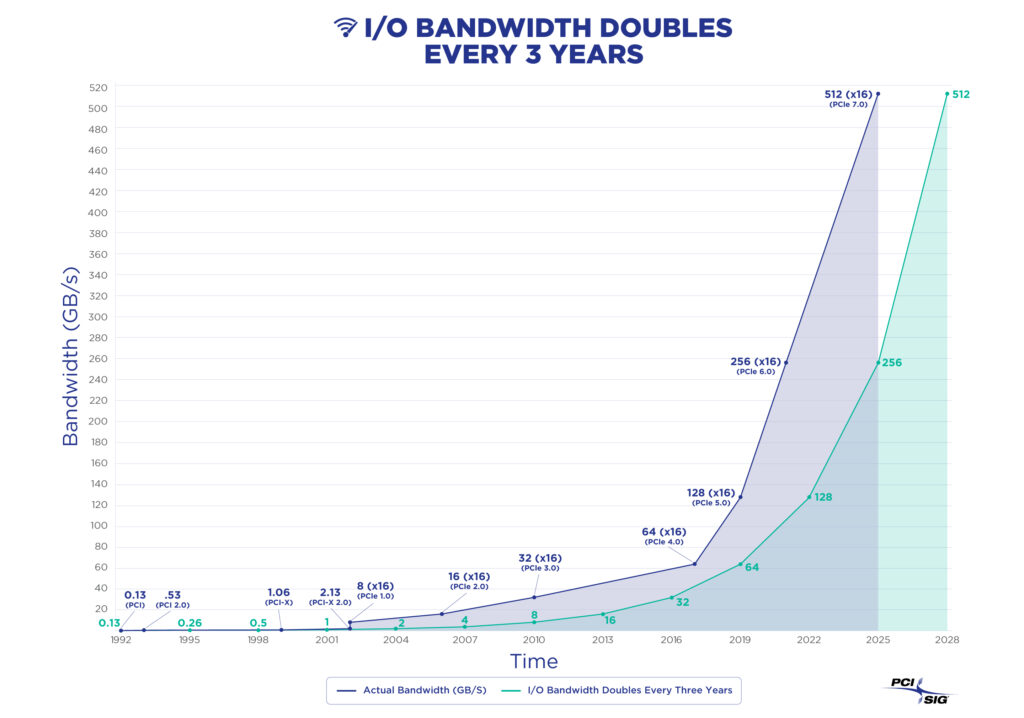

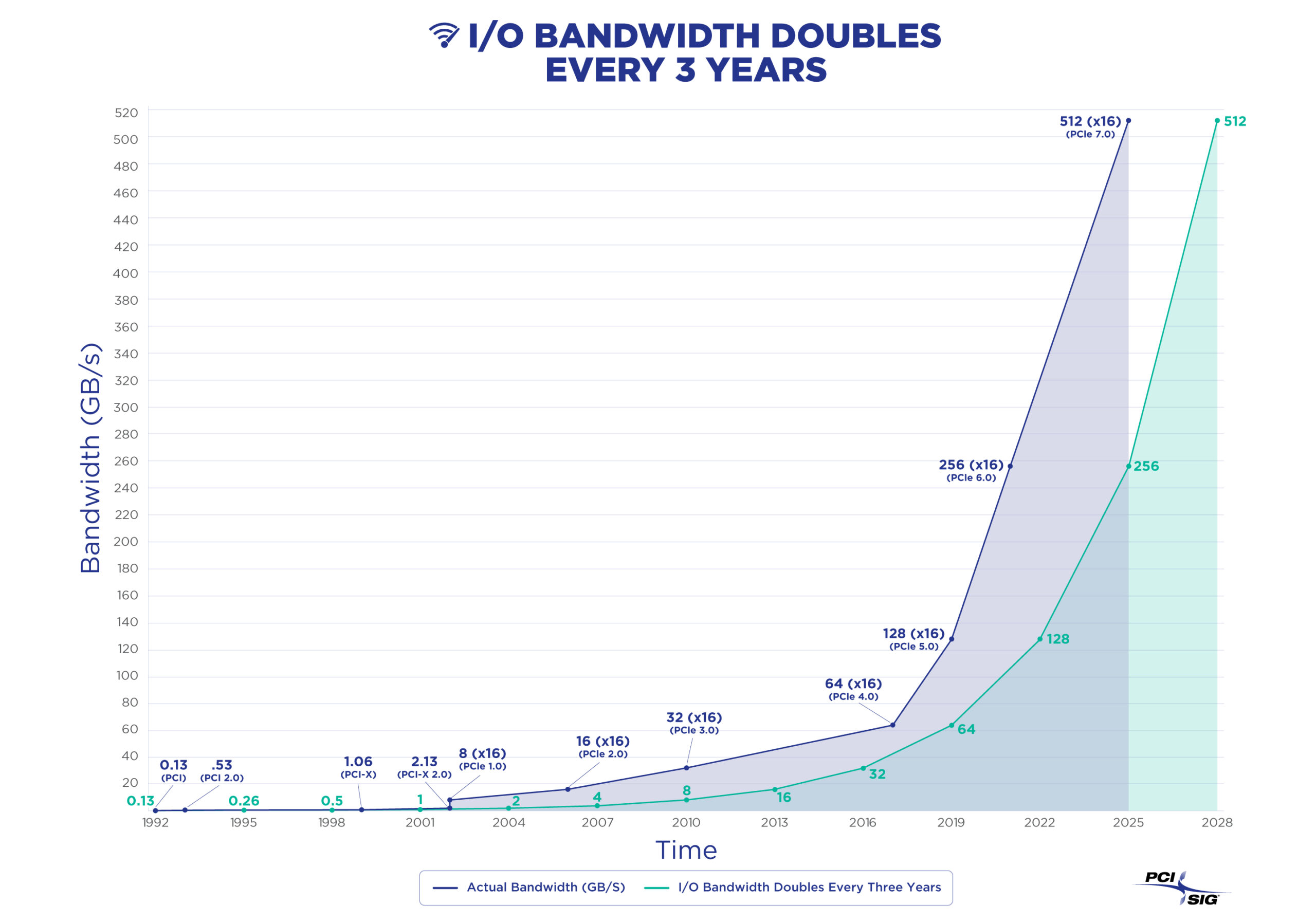

PCIe規格はPCI-SIG(PCI Special Interest Group)という業界団体が中心となって策定しています。この団体は半導体メーカー、システムベンダー、OEMなどの協力によって成り立っています。主に、新規格の標準化に向けて技術的検証、議論、仕様策定を行います。

PCIe 7.0規格は、2025年の正式リリースを目標に開発が進められており、既存の規格との下位互換性も維持される予定です。とはいえ、そのほとんどは業務用であり、一般に普及するには数年かかる見込みです。

信号方式の違い

NRZ(Non-Return-to-Zero)

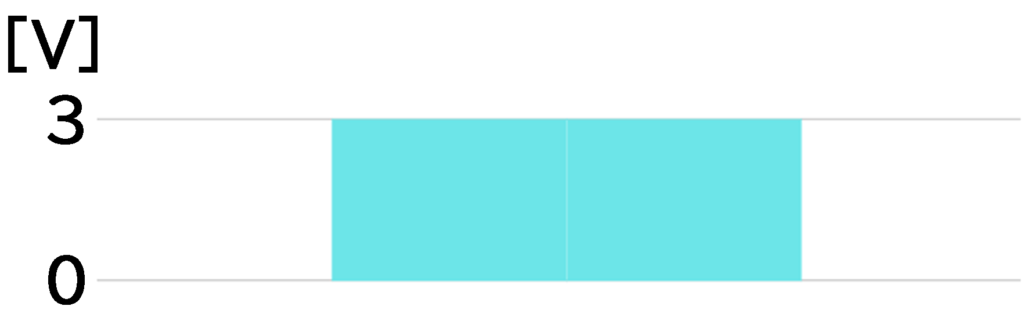

従来のPCIe 5.0規格まではNRZという信号方式が使われていました。これは1ビットあたり1つの電圧レベルを使用し、「0」と「1」の情報を表現する方式です。PCIe 5.0まではこれで32 GT/sの速度を実現していました。

PAM4(Pulse Amplitude Modulation 4-level)

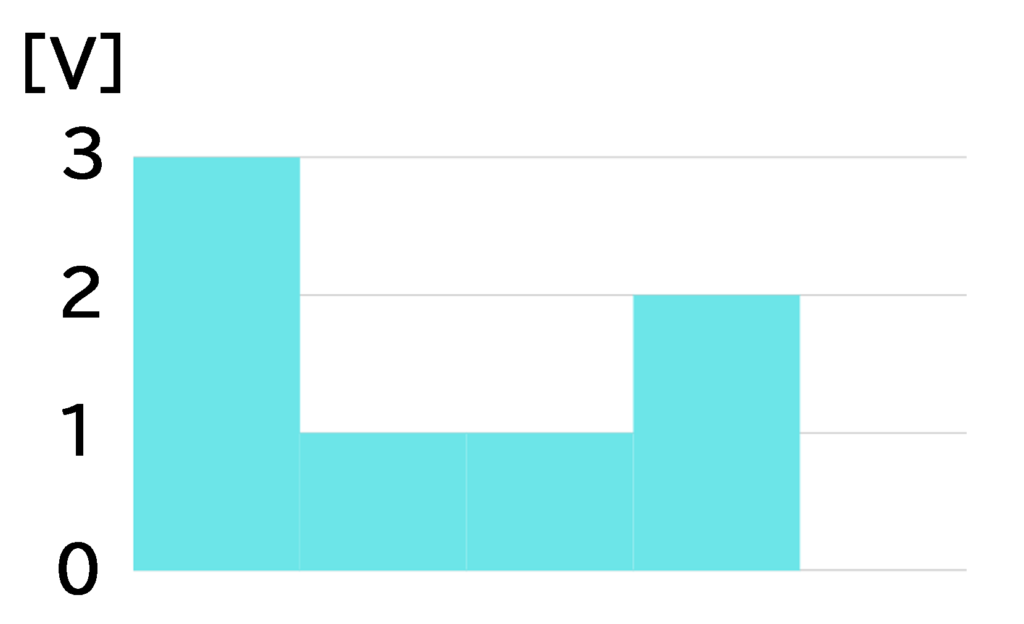

一方、PCIe 6.0以降(PCIe 7.0含む)ではPAM4という新たな信号方式が採用されました。PAM4は1クロックサイクルで4つの異なる電圧レベル(例えば0V, 1V, 2V, 3V)を使用し、1回の信号で2ビットの情報を伝送可能とします。これにより帯域幅が飛躍的に向上し、PCIe 7.0では128 GT/sという非常に高速なデータ転送を実現しています。

PAM4方式の課題と解決方法

PAM4は電圧レベルが細かく分割されているため、ノイズの影響を受けやすく、誤り(エラー)が増えやすいという課題があります。これに対処するため、PCIe 7.0では以下の技術的対策が施されています。

- 前方誤り訂正(FEC:Forward Error Correction) 冗長なデータを送信時に付加し、受信側で一定範囲の誤りを修正可能にする。

- 高度な信号処理(DSPやイコライゼーション) ノイズや信号劣化をリアルタイムに除去・補正し、安定したデータ受信を実現する。

- ハードウェア設計の改善 低損失のケーブル・基板素材やクロストーク低減設計を採用。

- クロック同期技術の向上 精密なクロック同期(PLLなど)により、受信タイミングのズレを最小化。

これらの技術により、PCIe 7.0では実用的な信頼性を持つ高速通信を実現しています。

なぜこんな高速通信が必要なのか?

なぜこれほどの高速通信が必要となるのか?その理由としては、AIや機械学習、ビッグデータ解析、クラウドコンピューティングなど、膨大なデータを高速かつ効率的に処理するニーズが急増しているためです。

また、800Gイーサネットや次世代の高性能コンピューティング(HPC)の普及も高速通信インターフェースの必要性を加速しています。PCIe 7.0はこれらの技術基盤として非常に重要な役割を担っています。

まとめ

PCIe 7.0は、次世代コンピューティングの中心となる規格であり、従来の技術的限界を超えるためのさまざまな新技術を採用しています。今後、この新規格がどのように私たちのデジタル環境を変えるのか、注目が集まっています。

参考資料

- PCI-SIG公式サイト: https://pcisig.com

- 「PCIe 7.0規格発表の記事」PC Watch: https://pc.watch.impress.co.jp/docs/news/1656229.html

- 「PAM4技術の詳細解説」fs.com: https://www.fs.com/jp/blog/what-is-the-meaning-and-difference-between-pam4-and-nrz-13749.html

コメント